Halvledarföretaget Renesas Electronics har utvecklat 22nm kretsteknologier för ett embedded spin-transfer torque magnetoresistiv random-access (STT-MRAM) testchip med med snabba läs- och skrivmöjligheter.

Chipet är tillverkat med en 22-nm-process och inkluderar en mikrostyrenhet och en 10,8 megabit inbäddad MRAM-cellmatris. Den uppnår en slumpmässig läsåtkomstfrekvens på över 200 MHz och en skrivkapacitet på 10,4 megabyte per sekund (MB/s).

Allt eftersom IoT- och AI-teknologier fortsätter att utvecklas förväntas MCU:er som används i ändpunktsenheter leverera högre prestanda än någonsin. CPU-klockfrekvenserna för högpresterande MCU:er ligger på hundratals MHz, så för att uppnå högre prestanda måste läshastigheterna för inbyggt icke-flyktigt minne ökas för att minimera gapet mellan dem och CPU-klockfrekvenserna.

MRAM har en mindre läsmarginal än flashminnet som används i konventionella MCU:er, vilket försvårar höghastighetsläsning. Å andra sidan är skrivprestanda för MRAM snabbare än flashminne eftersom det inte kräver någon raderingsoperation innan skrivoperationer utförs. Att förkorta skrivtiderna är dock önskvärt inte bara för dagligt bruk, utan också för kostnadsreduktion av skrivtestkoder i testprocesser och skrivning av kontrollkoder av slutprodukttillverkare.

För att möta dessa utmaningar har Renesas utvecklat nya kretsteknologier för att uppnå snabbare läs- och skrivoperationer i MRAM.

Snabb lästeknik

MRAM-avläsning utförs vanligtvis av en differentialförstärkare (avkänningsförstärkare) för att bestämma vilken av minnescellströmmen eller referensströmmen som är störst. Men eftersom skillnaden i minnescellströmmar mellan 0- och 1-tillstånden (läsfönstret) är mindre för MRAM än för flashminne, måste referensströmmen vara exakt placerad i mitten av läsfönstret för snabbare avläsning. Den nyutvecklade tekniken introducerar två mekanismer. Den första mekanismen riktar in sig på referensströmmen i mitten av fönstret i enlighet med den faktiska strömfördelningen av minnescellerna för varje chip som uppmätts under testprocessen. Den andra mekanismen minskar avkänningsförstärkarens offset. Med dessa justeringar uppnås snabbare läshastighet.

Vidare, i konventionella konfigurationer, finns det en stor parasitisk kapacitans i kretsarna som används för att styra spänningen på bitlinan så att den inte stiger för högt under läsoperationer. Detta saktar ner läsningsprocessen, så ett Cascode-anslutningsschema har introducerats i kretsen för att minska parasitisk kapacitans och snabba upp läsningen. Renesas uppger att tack vare dessa framsteg så kan man uppnå världens snabbaste slumpmässiga läsåtkomsttid på 4,2 ns. Även med hänsyn till inställningstiden (setup time) för gränssnittskretsen som tar emot MRAM-utgångsdata, kan företaget realisera en slumpmässig läsoperation vid frekvenser över 200 MHz.

Snabb skrivteknik

När det gäller skrivoperationer till STT-MRAM vid höga hastigheter så utvecklades tekniken i december 2021 med en förbättrad skrivgenomströmning genom att först applicera skrivspänning samtidigt på alla bitar i en skrivenhet med en relativt låg skrivspänning som genererades från den externa spänningen (IO-power) för MCU-chipet genom en nedtrappningskrets, och använde sedan en högre skrivspänning endast för de återstående få bitarna som inte kunde skrivas. Den här gången tar Renesas med i beräkningen att eftersom strömförsörjningsförhållandena som används i testprocesser och av slutprodukttillverkare är stabila, kan den nedre spänningsgränsen för den externa spänningen mildras. Genom att ställa in den högre nedtrappningsspänningen från den externa spänningen som ska appliceras på alla bitar i den första fasen, kan skrivgenomströmningen förbättras 1,8 gånger.

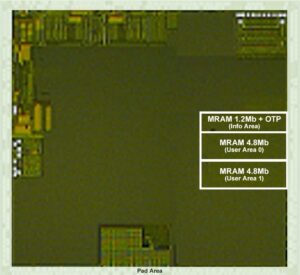

Genom att kombinera ovanstående nya teknologier tillverkades ett prototyp-MCU-testchip med en 10,8 Mbit MRAM-minnescellsuppsättning med en 22 nm inbäddad MRAM-process. Utvärdering av prototypchipet bekräftade att det uppnådde en slumpmässig läsåtkomstfrekvens på över 200 MHz och en skrivkapacitet på 10,4 MB/s vid en maximal övergångsstemperatur (JT) på 125°C.

Testchipet innehåller också en 0,3 Mbit OTP som använder MRAM-minnescelluppdelning för att förhindra förfalskning av data. Detta minne kan användas för att lagra säkerhetsinformation. Att skriva till OTP kräver en högre spänning än för att skriva till MRAM, vilket gör det svårare att utföra skrivning i fält, där nätspänningarna ofta är mindre stabila. Men genom att undertrycka parasitmotstånd i minnescellsmatrisen gör denna nya teknologi också skrivning i fält möjligt.