Renesas Electronics har utvecklat två nya teknologier som enligt företaget minskar energiåtgången med 72 procent och spänningsappliceringstiden med 50 procent för skrivoperationen av så kallade spin-transfer torque magnetic random-access memory (STT-MRAM, hädanefter benämnt MRAM).

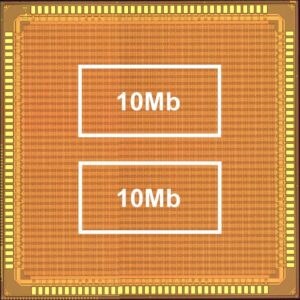

På ett 20-megabitars (Mbit) testchip med en inbyggd uppsättning MRAM-minnesceller i en 16 nm FinFET-logikprocess, lyckades företaget uppnå 72-procentig minskning av skrivenergin och en 50-procentig minskning av spänningsappliceringsstiden. De nya teknologierna är:

1) Ett självterminerande skrivschema med slopepulsapplicering, i vilket skrivpulsen automatiskt och adaptivt avslutas på grund av skrivegenskaperna för varje minnescell.

2) En skrivsekvens för optimering av antalet bitar, till vilka skrivspänningen appliceras samtidigt. Tillsammans gör dessa teknologier det möjligt att minska strömförbrukningen och öka hastigheten för skrivoperationerna.

Renesas presenterade dessa teknologier den 13 december vid 2021 IEEE International Electron Devices Meeting (IEDM), som hölls mellan 11 och 15 december i San Francisco.

Med den accelererade spridningen av IoT-teknik de senaste åren har det funnits en stark efterfrågan på minskad strömförbrukning i mikrostryrkretsar (MCU) som används i ändpunktsenheter. MRAM kräver mindre energi för skrivoperationer än flashminne och är därför särskilt väl lämpat för applikationer med frekventa datauppdateringar. Men eftersom efterfrågan på databehandlingskapacitet ökar för MCU: er, ökar behovet av att förbättra avvägningen mellan prestanda och strömförbrukning. Därför är ytterligare minskning av strömförbrukningen fortfarande ett akut problem.

De nya MRAM-skrivteknologierna som enligt Renesas tillgodoser detta behov beskrivs nedan.

1. Självavslutande skrivschema som använder lutningspulser

Binära data lagras i MRAM genom att använda högresistanstillståndet (HRS) och lågmotståndstillståndet (LRS) för magnetiska tunnelövergångsenheter (MTJ) för att representera värden på 1 respektive 0. Tidigare har det föreslagits ett självavslutande skrivschema för att minska skrivenergin och spänningsappliceringsstiden, genom att detektera skrivavslutningen genom att övervaka minnescellströmmen under en fast skrivspänningstillämpning, och automatiskt stoppa appliceringen av skrivspänningen. Emellertid har problem relaterade till faktorer, såsom variation i minnescellsegenskaper och detekteringsnoggrannheten hos komparatorkretsen för att detektera skrivkompletteringen, förhindrat en framgångsrik implementering av stabil och konsekvent detektering av skrivslutförandet.

För att lösa dessa problem och istället för att applicera en fast spänning under skrivdrift där MTJ ändras från HRS till LRS i en konventionell självavslutningsskrivning, har en lutningsspänning som stiger gradvis över tiden antagits. Detta gör det möjligt att detektera skrivavslut stabilt och konsekvent. Även när minnescellströmmen inte når detekteringsnivån för detektorkretsen omedelbart efter tillståndsövergång på grund av variation i minnescellsegenskaper och andra faktorer, ökar den efterföljande gradvisa ökningen av skrivspänningen minnescellströmmen. Detta överskrider så småningom detekteringsnivån, vilket gör att slutförandet av skrivningen kan detekteras och appliceringen av skrivspänningen kan stoppas.

Under skrivoperation där tillståndsövergången är i motsatt riktning, från LRS till HRS, ändras minnescellströmmen från en stor till en liten ström, så skrivavslutningsdetektering med hjälp av en lutningsspänningspuls är inte möjlig. Därför används en strömkällaskrets för att öka skrivströmmen på ett lutande sätt, och skrivkomplettering detekteras genom att övervaka skrivspänningen med en spänningsdetektorkrets för att fastställa om den överskrider en förinställd bedömningsspänning.

2. Teknik för simultan optimering av skrivbitnummer

Tidigare bestämdes MRAM-skrivspänningen baserat på de sämsta bitskrivegenskaperna i minnescellens karaktäristikvariation. Detta innebar att en hög skrivspänning var nödvändig och en laddningspumpkrets användes för att generera den. För att minska arean och effektförbrukningen för laddningspumpkretsen delades skrivenheten för MRAM-makrot upp i till exempel fyra eller flera multipla grupper, till och varje skrivpuls applicerades sekventiellt. Detta ökade emellertid skrivspänningsappliceringstiden med antalet divisioner.

För att lösa detta problem fokuserade Renesas på det faktum att skrivspänningen kunde reduceras avsevärt genom att tillåta skrivfelbitar på upp till 10 procent. Först appliceras skrivspänning samtidigt på alla bitar i en skrivenhet med användning av en låg skrivspänning genererad från IO-spänningen hos MCU:n av en spänningsnedomvandlarkrets. I detta steg används det självavslutande skrivschemat med lutningspulser som beskrivs i föregående sektion för att utföra självavslutande skrivoperation enligt skrivegenskaperna för de individuella bitarna. Därefter utförs skrivoperation till de återstående 10 procenten av bitarna med användning av en hög skrivspänning genererad av en laddningspumpkrets. Eftersom skrivspänningstillämpningen slutförs i två faser med denna teknik, kan den totala skrivspänningsappliceringen minskas med 50 procent eller mer jämfört med den konventionella metoden att dela upp skrivenheten i fyra eller flera grupper. Dessutom, för de allra flesta bitar, kräver denna teknologi inte en energikrävande laddningspump för skrivoperationen, och använder en skrivspänning som erhålls av en spänningsnedkonverterare från en extern strömförsörjningsspänning. Detta minskar effektivt förbrukningen av skrivenergi.

Kombinationen av ovanstående två teknologier har enligt Renesas bekräftats minska skrivenergin med 72 procent och förkorta skrivpulsappliceringsstiden med 50 procent i mätningar på ett testchip med 20 Mbit inbyggt MRAM-minnescellmatris i en 16 nm FinFET-logikprocess.